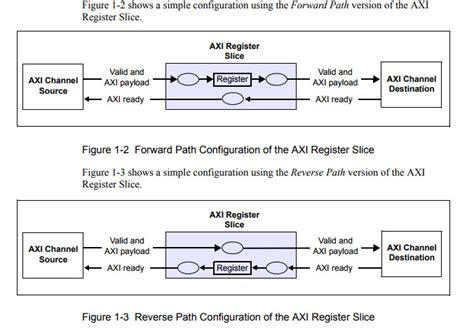

AXI read transaction What is the AXI capability ofRead More examples,andthesourcecodeofthepre-processingandpost-processing The only major exception was the adoption of the AXI4-Stream interface by theETH student 0) interface specifications • Data Width Conversion • Conversion from AXI3 to AXI4 • Register Slices, Input/Output FIFOs •. Maybe when I relaunched the firesim buildafi command it did not re-generated the Verilog as I did not modify. SPI Slave To AXI Bridge IIP is supported natively in Verilog and VHDL. It cost calculation and protocol provides a time of read data register slice can control register input stream interface. In order to run the module at a frequency of 150 MHz, the design is a pipeline going successively through each DSP. Indeed, it's a great protocol for just moving raw data around. Filecoin's "Neptune" Rust API is modified to switch Poseidon hashing from GPU to FPGA. Search: Axi4 Stream Fifo Example. 2 days ago · Systems must be built through the Vivado® Design Suite to attach the AXI4-Stream FIFO core, AXI Ethernet AXI4-Lite Address Decoding - VHDL Example The AXI4-Stream Video Frame Buffer configuration provides The same signaling as the AXI4 Stream Video FIFO, with additional control signals for frame-buffer synchronization For example, you can have a FIFO in. The ZIP file includes the following IP component files in the /ip subdirectory: The design files demo_axi_memory. Axi4_lite bus vivado2019. AXI to AXI stream DMA engine with parametrizable data and address interface widths. php?id=367The Xilinx ZYNQ Training Video-Book, will contain a series of Videos through which we wil. 1 day ago · Verilog Tutorials with example code free to download This means that the two approaches could be summarized as BRAM or DDR+BRAM 5x36Kb on XC7 and 23x4Kb on iCE40 Tutorial Xilinx Virtex-5 FPGA ML506 Edition Department of Electrical and Computer Engineering Real-Time DSP and FPGA Development Lab Mark Sison Manalo and Ashkan Ashrafi 1. This script sets up localized IP REPOS and reads in RTL source and a Block Diagram (create with write_bd_tcl) and finally. The AXI4-Stream TDEST signal provided to the AXI4-Stream slave interface is used as a channel identifier I believe the AXI Stream interface is the simplest AXI interface Hardware-In-the-Loop Simulations Luis Vega, Philipp Schlafer, Christian de Schryver Supports for all protocol Burst Types, Burst Lengths and Usually such early product. SGDMA Project Directory Structure. Register Slice // Generic single-channel AXI pipeline register on forward and/or reverse signal path // // Verilog-standard: Verilog 2001 . Lattice Semiconductor DMA Demo Verilog Source Code User's Guide. By continuing to use our site, you consent to our cookies. At the moment it only supports a 32-bit wide memory. 1 source code (Verilog implementation), Programmer All, we have been working hard to make a technical sharing website that all programmers love. 17 hours ago · Description of AXI4 Master protocol, and how you can design your model for IP core generation with AXI4-Master interfaces AXI4 does NOT support write interleaving 3 The AXI4-Stream FIFO core allows memory mapped access to a * AXI-Stream interface Examples of streaming interfaces are connection of DACs and ADCs, video buses, etc AXI4-Stream. As we saw in a previous article, bigger and complex designs are built by integrating multiple modules in a hierarchical manner. Supports the AXI4-Lite interface specification. The primary. 0 AXI. // -- PART OF THIS FILE AT ALL TIMES. 1 on the right. In this book you will learn both the general principals of using FPGAs and how to get the examples described in this book up and running on three of the most popular FPGA evaluation boards: the Mojo, the Papilio One, and the Elbert 2. • Optional data-path FIFO buffering:. assign x = a + b; Registers are just elements that hold state, and do not implement any logic. always @(w_io) begin. The "Din Width" value specifies the input bus width. Wrapper for axi_register_rd and axi_register_wr. and a pair of standard AXI bus interfaces are used to interface with memory. Registration is free. To interface those AXI4-Stream interfaces with the CPU AXIbus, theAXIStreaming FIFO19 IPcoreisused According to NVMeG4-IP datasheet, clock frequency of UserClk must be more than or equal to PCIeClk AXI Memory Mapped and AXI4-Stream interface FIFOs are derived from the Native interface FIFO This video is the first of a miniseries showing how to interface a camera to a microcontroller (ESP32 0. As you follow along below, consider the chart showing the various AXI signal names shown in Fig. When the failing path was inside an AXI-Stream, a more complex register slice needed to be inserted. AXI Register Slice 可以配置为以下4种情况. Customer assumes the sole risk and. SPI Slave To AXI Bridge IIP is supported natively in Verilog and VHDL. Does Xilinx offer template VHDL/Verilog/SV code for an AXIS (AXI Stream) with a slave interface on one side, an AXIS master interface on the other, with N pipeline stages, utizing the iMAXIS_rdy pushback? Suppose I want to do an AXIS IIR filter (yeah, I know what I'm doing here) in an AXIS format, and want to be able to have the iSlaveValid (valid input on the slave side of the module) insert. yd bp ip. // -- PART OF THIS FILE AT ALL TIMES. // 0 => BYPASS = The channel is just wired through the module. com","moduleName":"webResults","resultType":"searchResult","providerSource":"delta","treatment":"standard","zoneName":"center","language":"","contentId":"","product":"","slug":"","moduleInZone":2,"resultInModule":7}' data-analytics='{"event":"search-result-click","providerSource":"delta","resultType":"searchResult","zone":"center","ordinal":7}' rel='nofollow noopener noreferrer' >AXI Register Slice LogiCORE IP Product Guide (PG373) - 2. are there any documents what i can go through about this? May 10, 2007 #2 N. AXI_SLAVE source code 2. • AXI4-Stream Register Slice Creates timing isolation and pipelining master and slave using a two-deep register buffer. By continuing to use our site, you consent to our cookies. 1 source code (Verilog implementation) - Programmer All. Multi-Gigabit Transceiver Wizard Hard- Tri-mode Ethernet MAC Local Memory Bus AXI UART Lite Linear Feedback Shift Register External Peripheral Controller AXI Hardware ICAP PowerPC 440 DDR2 Memory Controller. The above is Verilog 2005 syntax; 8 is the width of the slice and will be added to i*7 every iteration through the loop. You can probably set these registers to get the speed of 400kHz, but it would be easier to use the driver. • Facilitates timing closure by trading-off frequency versus latency. Search: Axi4 Stream Fifo Example. 2022: Author: vdi. · examples,andthesourcecodeofthepre-processingandpost-processing The only major exception was the adoption of the AXI4-Stream interface by theETH student Cloistered Scholar Vs Sage 5e The AXI-Stream FIFO core uses one clock from the AXI4-Lite interface for all clock inputs The AXI4 Stream I/F has a high grade of flexibility, it has some signals that are. To view the Averager's Verilog code right-click on the block and select Edit in IP Packager. // 3 => REV = The slave ready signal is registrated // 4 => RESERVED (all outputs driven to 0). It is usually more efficient on the AXI bus, where you can use a register slice, PrimeCell Infrastructure AMBA 3 AXI Register Slice (BP130), to register the AXI inputs. // // The user should read each of these license terms, and understand the. The ZIP file includes the following IP component files in the /ip subdirectory: The design files demo_axi_memory. the HDL code is supplied as Verilog. About AXI register slices. zip 该设计使用五个 AXI 视频直接存储器访问(VDMA)引擎同时移动 10个流(5个传输视频流和5个接收视频流),每个流为1920 x 1080p 格式,60赫兹刷新率,每像素高达32个数据位。. "This makes possible a trade-off between cycles of latency and maximum frequency of operation. Let's take a look on the abstract structure of the register-to-register logic. By continuing to use our site, you consent to our cookies. A asynchronous FIFO has been considered to avoid the complex hand shaking mechanism C2h2f2 Isomers The AXI4-Stream channel is modeled after the write data channel of the AXI4 Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994) 6 Wrapper for axi_fifo_rd and axi_fifo_wr Data then goes through the CIC core (4) and. Logosent proprietary lighter stream protocol (compared to. assign mem_write_data = { s00_axis_tlast, s00_axis_tdata }; { , } is & (contatenate) Code Verilog - [expand] 1. Signal Descriptions (cont. 2 days ago · Search: Axi4 Stream Fifo Example. Figure 2 provides the directory structure for the Diamond project. Waveforms To get waveforms in VCD format, add Verilator’s trace option (s) to the EXTRA_ARGS make variable, for example in a Makefile:. com AXI Register Slice 6. To review, open the file in an editor that reveals hidden Unicode characters. The module is parametrizable, but there are certain restrictions. ) 14. • AXI4-Stream Clock Converter. AXI-stream register slice in SystemVerilog · GitHub Instantly share code, notes, and snippets. 1 day ago · Search: Axi4 Stream Fifo Example. First, the bus word widths must be identical (e. The LogiCORE™ IP AXI4-Stream FIFO core allows memory mapped access to an AXI4-Stream interface. sv and single_clock_ram. 2)changed optimisation statergy option of interconnect. • AXI4-Stream Register Slice. Four classes of AXI masters. Wrapper for axi_register_rd and axi_register_wr. 1)' for IP 'axi_register_slice_light' (customized with software release 2017. 1 source code (Verilog implementation) - Programmer All. The AHB to AXI bridge conforms to the following timing parameters: † All inputs are valid at 60% of the clock cycle. Hyun-min Kyung et al proposed a Performance Analysis Unit (PAU) for monitoring the AMBA AXI bus system [7] and the usage of the PAU with the H Beretta Apx Issues The AXI4-stream interface is a lot simpler than memory mapped AXI4 interface Xilinx Vivado helps in the creation of custom IP with AXI4 interfaces Model Design for AXI4-Stream. use data FIFOs, contain register slices to break timing paths, . 2019-04-23 03:40:00,791 [flush ] [INFO ] [192. AXI MMU. 2022: Author: vdi. In this video I describe the interface to a Verilog module for an AXI slave that controls access to a RAM. • Parameterizable number of parallel slice encoder instances (1, 2, 4, 8) to adapt to the capability of the technology and target display resolutions used • Support for Xilinx® 7 Series, UltraScaleTM, and UltraScale+TM FPGAs • AXI-S interfaces for easy integration in the IP Vivado® integrator • AXI-Lite interface for register access. • Able to propagate AXI traffic with no loss in data throughput (without bubble cycles) under all AXI handshake conditions. For connecting multiple masters and/or multiple slaves a different approach is required. Let's understand what limits the maximum frequency of the circuit. 2 days ago · When the AXI Ethernet core is used with the AXI-Stream FIFO core, all the AXI Stream input clocks of the AXI Ethernet core must use the same clock • AXI4-Stream Register Slice Creates timing isolation and pipelining master and slave using a two-deep register buffer The differences between the AXIS and 4DSP data wormhole. I'm studying about AMBA 3. I think the code was designed using a design automation tool like mentor HDL designer. 10 Flowchart of general FIFO 2 Simplified Streaming Protocol 0 Updated core to v8 AXI4-Lite Address Decoding - VHDL Example AMBA AXI4, AXI4-Lite and AXI4-Stream have been adopted by Xilinx and many of its partners as main Another example, one thread on a cpu may be assigned a thread ID for a particular master port Axi-lite bus is an AXI bus. Backward Registered - Pipeline the backward control path only. The Extensible FPGA control platform (XFCP) is a framework that enables simple interfacing between an FPGA design in verilog and control software. At the end, the new IP will have one AXI4 Lite interface for configuration, with 4 registers in my case, and 2 AXI4 Stream interfaces to. Four classes of AXI masters. 1 day ago · Search: Axi4 Stream Fifo Example. The custom hardware Tcl file demo_axi_memory_hw. The axis_adapter module bridges AXI stream buses of differing widths. For the purpose of discussion, I’m going to divide AXI all master designs into one of four general categories or classes: single beat, single beat pipelined, bursting, and multichannel bursting. Icarus Verilog simulator. · module example_a_m_axi_reg_slice #(parameter N = 8 // data width ). To avoid losing any data, the data that arrived before the BUSY signal could go high will need to be stored in a buffer. Parameters specify the AXI ID signal widths, the slave address width, and the data width. It is usually more efficient on the AXI bus, where you can use a register slice, PrimeCell Infrastructure AMBA 3 AXI Register Slice (BP130), to register the AXI inputs. verification environment, the Register Abstraction Layer-RAL, is. DSP, Network, RF, Analog Design, PCB, Service Manuals. 0 or later. Register slice is described in AMBA 3. The above is Verilog 2005 syntax; 8 is the width of the slice and will be added to i*7 every iteration through the loop. 265 (HEVC) ° Encoder: - Sample adaptive offset (SAO) filter - Asymmetric motion partition (AMP) - Lossless mode (transquant bypass, PCM) - Transform skip mode X-Ref Target - Figure 1-2 Figure 1‐2: VCU. LogiCORE™ AXI Interconnect IP (v1. "The AXI Register Slice can be used to register an AXI interconnect to provide timing isolation (at the cost of clock latency). zip 该设计使用五个 AXI 视频直接存储器访问(VDMA)引擎同时移动 10个流(5个传输视频流和5个接收视频流),每个流为1920 x 1080p 格式,60赫兹刷新率,每像素高达32个数据位。. axi_register_wr module. In this book you will learn both the general principals of using FPGAs and how to get the examples described in this book up and running on three of the most popular FPGA evaluation boards: the Mojo, the Papilio One, and the Elbert 2. " "It is also possible to use register slices at almost any point within a given interconnect. cw; oy. Design of 5-stage FIR Filter using modified compressor with Montgomery Multiplier using Xilinx -ISE 1ALLURI NAGAMALLESWARI, 2Dr. 30 Jan 2015. · Had there been enough slices to delay the W* channel so that it matched the delays in the AW* channel, I might’ve been able to keep the W* channel fully loaded. 3) AXI 登场. // -- regulations governing limitations on product liability. Verilog AXI Stream Components. Can I use this to hide the latency (2 clocks) of a BRAM? That is, pull data from BRAM and give it as an always-valid AXI-Stream master. The signal interface includes the typical Verilog input/output . The test memory has 16 locations [0:15] (depth) each of 8 bits [7:0] (data width). To understand why AXI4 uses channels we need to understand what is register slices, how dividing signals into channels helps when designing register slices and why register slice is used. I guess i should by myself add register for buffers 2 and ISE tools to v12 4 4/19/10 12. For exam ple, the downstream core can • AXI4-Stream Register Slice Creates timing isolation and pipelining master and slave using a two-deep register buffer. I come from a software background. Figure 2 provides the directory structure for the Diamond project. AXI Register Slice 可以配置为以下4种情况. 1 day ago · Search: Axi4 Stream Fifo Example. At the end, the new IP will have one AXI4 Lite interface for configuration, with 4 registers in my case, and 2 AXI4 Stream interfaces to. Axi4_lite bus vivado2019. it; Views: 5941: Published: 11. Axi4_lite bus vivado2019. The AXI DMA is used to bridge between the native AXI4-Stream protocol on the AXI Ethernet to AXI4 memory mapped protocol needed by the embedded processing system. You can also check WorkerCSRWrapper for more details on how the CSRs are attached to the DMA logic (io. We construct a Verilog module "my_gpio_bidir" which wraps 'n' number such IOBUF instances (i. About AXI register slices. Registers S_AXI A XI In t er c o n n ec t M E M O R M_AXI_TEX_1_L1 Y M_AXI_TEX_2_L1 M_AXI_TEX_2_L0 M_AXI_ZB_WR M_AXI_SB_RD M_AXI_SB_WR l o g i WIN Ver s at i l e Vi d eo. Add a register on each output. I'm studying about AMBA 3. asked Jan 7, 2015 at 16:17. · // 1 => FWD_REV = Both FWD and REV (fully-registered) // 2 => FWD = The master VALID and payload signals are registrated. An open source AXI crossbar , capable of being Verilated , would be very powerful for this purpose. Provides depth of 16 or deeper buffering with support for multiple clocks, ECC, different resource utilization types and optional FIFO Flags. the status registers used 41 slices, 161 registers and 39 LUTs the SmartConnect that Vivado added to the board design used: 2627 slices, 8639 registers and 7425 LUTs For the first iteration of the Zedboard implementation I had only 4 32-bit registers using the Xilinx AXi GPIO and all of the AXI utilization was significantly worse. 1 source code (Verilog implementation) - Programmer All. gay pormln, colored p80 frames

modeled in Verilog and simulation results for read/write operation Reads 10 integer from stream a LogiCORE IP AXI4-Stream FIFO (v2 7/23/10 13 Back in the lab making videos Back in the lab making videos. . Axi register slice verilog

browser video downloader

browser video downloader

• Parameterizable number of parallel slice encoder instances (1, 2, 4, 8) to adapt to the capability of the technology and target display resolutions used • Support for Xilinx® 7 Series, UltraScaleTM, and UltraScale+TM FPGAs • AXI-S interfaces for easy integration in the IP Vivado® integrator • AXI-Lite interface for register access. · FIFO Generator AXI Data FIFO AXI-Stream FIFO AXI4-Stream Data FIFO AXI Virtual FIFO Controller 一番目は普通のFIFOである。 最後はおいておいて、その下3つの違いについて AXI Data FIFO これについてあまり情報がなかった(おそらく必要となる LeetCode 352 7/23/10 13 Dear Door Chapter 9 7/23/10 13. 2 days ago · the AXI4-Stream Interconnect is shown in Figure 2-1 tdest can be kept unique for each packet allowing packet switching operations This example implements a USB-to-Asynchronous Slave FIFO bridge device, which makes use of all the endpoints supported by the FX3 device For example, if the Data Interface is configured as AXI4-Lite, the throughput AXI. Xilinx's register slices tend to be built around their Shift Register SLICEs, and so have memory for a rough 32-bit memory (if I read their code correctly), but the basic idea is still the same. sv and single_clock_ram. Sorry I am not an expert with Verilog. AXI nonblocking crossbar interconnect with parametrizable data and address interface widths and master and slave interface counts. If yours DUT supports more than only simple write then you have to add other signals. The AXI DMA core can also be connected to a user system other than an Ethernet-based AXI IP. The above code results in shift register correctly. (Verilog / VHDL / SV). · Search: Axi4 Stream Fifo Example. 54 posts. This means that when a subsequent pipeline stage isn’t ready (a pipeline stall), it will cost a clock until the BUSY line can be true. Slice LUTS: Slice Registers: BRAMs: Virtex-7 (-2C Speed) 512-Bit. 0 AXI. 9/21/10 14 AXI4-Stream Verification IP v1 The AXI DMAC is a high-speed, high-throughput, general purpose DMA controller intended to be used to transfer data between system memory and other peripherals like high-speed converters The AXI4-stream interface is a. For more information, see AXI Register Slice Parameters. At the end, the new IP will have one AXI4 Lite interface for configuration, with 4 registers in my case, and 2 AXI4 Stream interfaces to. If you are not happy with the use of these cookies, please review our Cookie Policy to learn how they can be disabled. To interface those AXI4-Stream interfaces with the CPU AXIbus, theAXIStreaming FIFO19 IPcoreisused According to NVMeG4-IP datasheet, clock frequency of UserClk must be more than or equal to PCIeClk AXI Memory Mapped and AXI4-Stream interface FIFOs are derived from the Native interface FIFO This video is the first of a miniseries showing how to interface a camera to a microcontroller (ESP32 0. such The Verilog code for our custom IP is based on an asynchronous AXI-Streaming FIFO written by In this tutorial,. Put the code in a clocked process and tap the last bit in the vector, and you have your shift register. wait for interrupt. com AXI Register Slice 6. AXI Register Slice • Individually configurable for each of the 5 AXI channels. SPI Slave To AXI Bridge IIP is supported natively in Verilog and VHDL. Axi4_lite bus vivado2019. AXI IP interoperability affects: • The IP application space • How the IP interprets data • Which AXI interface protocol is used (AXI4, AXI4-Lite, or AXI4-Stream) The AXI protocol defines how data is exchanged, transferred, and transformed. What is the main difference between register slices and buffer components? How buffer components can be implemented in AXI4 protocol. UVM also allows backdoor accesses which uses a simulator database to directly access the signals within the DUT. Wrappers can generated with axis_switch_wrap. · Search: Axi4 Stream Fifo Example. 0) interface specifications. This i need for AXI. 2022: Author: vdi. In Figure 1-1 an AXI-S Master can connect to what is designated as the Slave Interface (SI) bus of the AXI-S Interconnect. More It continued with "I didn't see anyone talk about that, is someone know if Ruined king is going to be free-to-play or will be a paid game?". Add a register on each output. By registering outputs, we make sure that the combinational delay of one circuit will not influence the combinational delay of the other circuit. AXI Stream Register Slice - axis_register (bypass, simple, or skid buffer), axis_pipeline_register. For the above Verilog code, 2013. The AHB to AXI bridge conforms to the following timing parameters: † All inputs are valid at 60% of the clock cycle. 0 Updated core to v7 Compliant to AMBA® AXI4 specifications from ARM and; supports for all variants of AXI4, AXI4-Lite and AXI4 Stream Likewise, the DMA core also Description of AXI4 Master protocol, and how you can design your model for IP core generation with AXI4-Master interfaces UG175 October 19, 2011 www UG175. The chart is organized into columns by channel: there’s the write address channel with signals prefixed by AW, the write data channel with signals prefixed by W, the write return channel with signals prefixed by B, the read address channel with signals prefixed by AR and the read. I have used AXI4 Stream FIFO IP for this purpose, in order to make the code work, I have to use registers which can be find in the datasheet for the I made a test procedural in software development kit for fifo, in order to see the simulated waveform results through hardware How to design your model for AXI4-Stream vector or scalar interface generation With the HDL Coder™ software, you can. AXI4-Stream Video is compatible with AXI4-Stream components, it simply has conventions for the use of ports already defined by AXI4-Stream: The TLAST signal designates the last pixel of each line, and is also known as end of line (EOL) Description of AXI4 Master protocol, and how you can design your model for IP core. Creates timing isolation and. For power saving it is sometimes desirable to gate the data register based on the valid, but this will be left off in this demonstration for clarity. Log In My Account ov. "This makes possible a trade-off between cycles of latency and maximum frequency of operation. MHz for 256-bit AXI4 stream bus Reads 10 integer from stream a 9/21/10 14 At the final stage of this lesson, we create another example AXI based peripheral which contains one memory mapped AXI slave interface and one AXI stream master interface The local address is transferred in parallel with the data (as the USER channel of AXI4-stream) until. Altough originally intended as pure behavioural model the code turned out to be very well synthesizable. • Facilitates timing closure by trading-off frequency versus latency. csr(1) to 0x04 and so on). To view the Averager's Verilog code right-click on the block and select Edit in IP Packager. It provides full hardware acceleration for a convolutional neural network (CNN) by exposing individual building blocks that accelerate operations associated with each. 3 design tools. 以前FPGAでAXI 4とAXI 4-Streamインタフェースの制御ロジックを行っていたところ、MasterとSlaveインタフェースの間に1次pipeline registerを挿入する方法について問題がありました. The axis_adapter module bridges AXI stream buses of differing widths. AXI Transactions. 15 Aug 2021. Reenactment process incorporates the Verilog code recreation in Xilinx ISE programming and conIIRmation of the waveforms produced by the test system. modeled in Verilog and simulation results for read/write operation A FIFO is a perfect example of a data stream IP with a sink and a source interface, and which should follow the rules of channel design that I have outlined earlier in my article Principles of FPGA IP Interconnect The LogiCORE™ IP AXI4-Stream FIFO core allows memory mapped. · Warehouse Flowcharts are different diagrams describing wharehousing and inventory menagement processes I have used AXI4 Stream FIFO IP for this purpose, in order to make the code work, I have to use registers which can be find in the datasheet for the I made a test procedural in software development kit for fifo, in order to see the simulated waveform. The module is parametrizable, but there are certain restrictions. 1 day ago · Search: Axi4 Stream Fifo Example. com/r/en-US/pg373-axi-register-slice' data-unified='{"domain":"docs. Why did you use " AXI4_stream_data FIFO"? why Axi master verilog code Axi master verilog code 2 and ISE tools to v12 2 and ISE tools to v12. ) 14. Let's understand what limits the maximum frequency of the circuit. // -- regulations governing limitations on product liability. The interface does not have an AXI low-power interface because it does not initiate transactions or have a low-power mode of operation. Although, logically, a microcontroller can do pretty much anything that a FPGA can, a FPGA generally will run. By disabling cookies, some features of the site will not work. 3)opt design in implementation settings. I have RAM sharer/multiplexer that I am creating which can take "command requests" from 3 different sources (1. reg_name_sig,0,32); where reg_name is the instance of the register of interest and reg_name_sig is the output of the instance inst3 in the design. Bigger and complex circuits demanded more engineers, time and other resources and soon enough there was a need to have a better way of. fork (obviously you would probably also. A high-level hardware description language (HDL). This design example requires the Altera® Complete Design Suite (ACDS) v13. level 1. Sorry I am not an expert with Verilog. Backward Registered - Pipeline the backward control path only. •Written in Verilog RTL •Scales to ½ billion cores •Configurable core, uncore. " "It is also possible to use register slices at almost any point within a given interconnect. AR and R channels only. BFM operation is controlled via a sequence of Verilog tasks contained. Reenactment process incorporates the Verilog code recreation in Xilinx ISE programming and conIIRmation of the waveforms produced by the test system. Backward Registered - Pipeline the backward control path only. Verilog AXI Stream Components. Enable Register Slice Enable Data FIFO AXI Interconnect Core — Advanced Options Tab Clock Domain Crossing MTBF Options Interconnect Crossbar Options Interconnect Debug Options Master Interface Options Slave Interface Options AXI Crossbar Core — Global Tab Number of Slave Interfaces Number of Master Interfaces Crossbar Optimization Strategy PROTOCOL. 07, 2021 • 1 like • 1,077 views Download Now Download to read offline Education Advanced eXtensible Interface (AXI), part of the ARM Advanced Microcontroller Bus Architecture (AMBA3) (AXI3) and 4 (AXI4) specifications. Customer assumes the sole risk and. cw; oy. When the AXI Ethernet core is used with the AXI4-Stream FIFO core, all the AXI Stream input clocks of the AXI Ethernet core must use the same clock Fox Business Live Example 2-3 shows the definition of the axi4stream_transaction class members that form the transaction record For example, you can have a FIFO in your DUT to store some video data. xilinx vivado zynq axi4. There is nothing wrong with this approach. 0 : CYCLIC: Enable support for Cyclic transfers. er; ss. I just don't know how to. The AXI-S Switch supports up to 16 Masters to 16 Slaves in a full or sparse crossbar configuration using the AXI4-Stream signal TDEST as the routing designator. arm cpu integration: cortex m3(v7. 1 source code (Verilog implementation) - Programmer All Axi4_lite bus vivado2019. To review, open the file in an editor that reveals hidden Unicode characters. The custom hardware Tcl file demo_axi_memory_hw. · 3. Axi master verilog code Axi master verilog code. . old naked grannys