This tutorial illustrated how to use the v++ command --vivado option to control Vivado synthesis and implementation, using a simple example to optimize the design with the Vivado tool. Sep 17, 2013 · Date. integrated design environment (IDE). Vivado 2021. The Vivado Design Suite replaces the ISE Design Suite. com","moduleName":"webResults","resultType":"searchResult","providerSource":"delta","treatment":"standard","zoneName":"center","language":"","contentId":"","product":"","slug":"","moduleInZone":2,"resultInModule":2}' data-analytics='{"event":"search-result-click","providerSource":"delta","resultType":"searchResult","zone":"center","ordinal":2}' rel='nofollow noopener noreferrer' >Vivado Design Suite Tutorial - Implementation | Xilinx

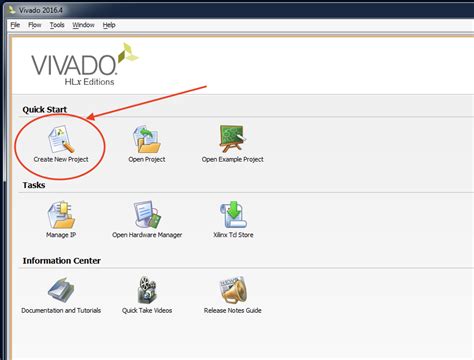

www. Click OK. Step 1: Creating a Project with the Vivado New Project Wizard. In my case, the directory is loacated at C:\Xilinx\Vivado\2013. Add the downloaded repository as a default IP repository to Vivado by specifying its search path to Vivado. Click Finish to create the Vivado project. Give the project the desired name and specify the desired file path. Configure easily your test bench: RTL. This support starts from the moment an investigator first makes contact with a victim, through to the. secret homemade voyeur wife sex videos. Training will be delivered by KCA and is available at three levels. ansible shell chdir. This document provides an introduction to using the Xilinx® Vitis™ unified software platform with the Zynq®-7000 SoC device. Best Korean Drama. Preparing the Tutorial Design Files. Launch Behavioral Simulation. Nov 21, 2022, 2:52 PM UTC a car starts from. Lab 1: Defining Timing Constraints and Exceptions. Give the project the desired name and specify the desired file path. Vivado implementation tutorial includes all steps necessary to place and route the netlist onto the FPGA device resources while meeting the logical, physical, and timing constraints of a design. 1: Linux Self Extracting Web Installer (BIN - 301. If you're a member of Bachelor Nation, you may want to know how to watch The Bachelorette 2022 live online for free to see who Gabby and Rachel choose in The Bachelorette season 19—and if it's the. Key Concepts. 4 , all OS(win和linux)「建议收藏」 思创斯忠实用户-ss • 2022年12月28日 16:31 • 未分类 • 阅读 10. Navigating Content by Design Process. #vivado #vitis #modelSim #questaSim #simulator #verilog #vhdl #fpga #productivity #programming #coding #xilinx #amd #shortsA quick glance at how to install. This Video is on "how to create Vitis/VIVADO 2020. FLATTEN_HIERARCHY}= {full}. By clicking next on the “ Project Type ” window in Figure 4 Vivado will open a new “Add source” window as in Figure 5. Create Vivado Project Start by sourcing the Vivado tools from the command line & launch the Vivado GUI: ~$ source /tools/Xilinx/Vivado/2021. - Brought-up first SystemVerilog support in Xilinx. Nov 10, 2021 · Step 1: Creating a Project with the Vivado New Project Wizard Step 2: Synthesize, Implement, and Generate the Bitstream Using the Synplify Pro Synthesis Tool and Vivado Design Suite to Debug a Design Step 1: Create a Synplify Pro Project Step 2: Synthesize the Synplify Project Step 3: Create DCPs for the Black Box Created in Synplify Pro. View focusolttraining _ Math Course 8 [2021-22] V2. 2 2020. mac mini server 2021; ceretropic mexico;. Mar 16, 2021 · vivado当前版本2018. 79K subscribers This Video is on "how to create Vitis/VIVADO 2020. Vivado Design Suite - 2021. The second file you’ll need is a TCL file. 3 which include the chipscope, the problem is : there are no ICON and ILA IP that constituted chipscope in Vivado IP Catalog , i added the ICON and ILA that generated in ISE14. Hardware Setup. 4 , all OS(win和linux)「建议收藏」 思创斯忠实用户-ss • 2022年12月28日 16:31 • 未分类 • 阅读 10. Add a MultiCycle Path. Step 4: Refer to UG973. If you're a member of Bachelor Nation, you may want to know how to watch The Bachelorette 2022 live online for free to see who Gabby and Rachel choose in The Bachelorette season 19—and if it's the. You will see that the tutorial and other directories, and the tutorial (Vivado) project file have been created. So I updated to Vivado 2021. The second file you’ll need is a TCL file. Preparing the Tutorial Design Files. pdf from MATHS 1175 MATHS1175 at Fanshawe College. 1) August 24, 2021. Hardware Setup. Jun 16, 2021 32 Dislike Share Explore Electronics 7. Vivado is the Hardware Development suite used to create a VHDL, Verilog, or any other HDL design on the latest Xilinx FPGA. I have not verified it in 2022. 1 in this project, but from what I can tell the same steps should apply in 2021. 1- Run the Vivado and create a project in the hardware folder with “zybo_z7_20_base_2021_1-vivado” name. I'm using Vivado 2022. Step through the popup menus to access the Default Part page. csv文件,这个表与vivado hardware manager中的器件一致。. There is a variety of step-by-step software tool tutorials to help you get working in the Vivado IDE quickly. 1 release update updated the supported devices and the compatible third. Add a MultiCycle Path. Connect the SZG-SENSOR board to Port A of the XEM8320 (this is important because this is where there reference design files from Opal Kelly expect it to be):. After that, you'll be able to work with them offline. Step 3: Creating Timing Constraints. Create Vivado Project Start by sourcing the Vivado tools from the command line & launch the Vivado GUI: ~$ source /tools/Xilinx/Vivado/2021. Third Party Licensing Guide: 06/03/2021: Key Concepts Date UG973 - Downloading the Vivado Design Suite Tools: 06/16/2021 UG973 - Installing the Vivado Design Suite Tools: 06/16/2021 UG973 - Obtaining and Managing a License: 06/16/2021. Getting Started with Vivado High-Level Synthesis. FLATTEN_HIERARCHY}= {full}. 21K subscribers #vivado #xilinx #verilog how to create project in Xilinx Vivado Tutorial | how to do simulation in Xilinx Vivado 2018. Lab 1: Defining Timing Constraints and Exceptions. The first file to download is the MicroZed board definition file, which should be extracted to your Xilinx implementation directory. Step 5: Add a Product Guide to the IP. Demonstrates building a Zynq UltraScale+ MPSoC processor-based embedded design using Vivado® Design Suite and the Xilinx® Software . The tutorials provide step by step instructions to perform specific design tasks in the tool using small example designs. CTM Tutorials tutorial 1 - 12; Proposal Sejarah tema pendidikan; Modul Ulang KAJI BM Kertas 2 SPM 2021 SET 2; Tugasan Kertas Kerja- Konsep Etika Dan Peradaban Menurut Perspektif Islam Dan Barat; Pemantapan Kesepaduan Nasional Malaysia; Kesan Tidak Menutup Aurat; ROLE PLAY Meeting Script 3; 4,0 Implikasi DAN Kepentingan Perlembagaan Persekutuan. This allows for design and tool setting modifications earlier in the design processes where they have less overall schedule impact, thus reducing design iterations and accelerating productivity. 1: Linux Self Extracting Web Installer (BIN - 301. Hardware Setup. 95 per trainee [as low as 0. 百度云分享 vitis vivado 2021. ② PC=PC+4+立即数*4,执行的. Analyze the Current Constraints Files. 找到“Text Editor”,并在右侧Current Editor下拉找到Custom Editor,并点击右侧的三个小点,选择路径;. Lab 1: Defining Timing Constraints and Exceptions. 4 , all OS(win和linux)「建议收藏」,希望您对编程的造诣更进一步. 2 2019. The Canadian women's soccer team boycotted training Saturday ahead of emergency talks with Canada Soccer in Florida. Jun 03, 2021 · UG973 - Vivado Design Suite Release Notes, Installation, and Licensing Guide. Hope this might help you. 2 English Vivado Design Suite User Guide Release Notes, Installation, and. Step 1: Opening the Example Project. Unit 1 . 1 project for basic GPIO interfacing on the Zynq Board". Pet Dog Puppy Obedience Training Treat Bait Food Snack Bag Pouch Dispenser. 86 P&P. 0 _ Math Content_FEVCT - 15 Grade 4 – Geomet. aining Site. We have showed demo with PYNQ Z1 FPGA board on this demo with. Step 1: Examine the Example Script Step 2: Starting Vivado with the Example Design Step 3: Synthesizing the Design Step 4: Launching the Vivado IDE Step 5: Defining Timing Constraints and I/O Planning Define Timing Constraints I/O Planning Step 6: Exporting the Modified Constraints Step 7: Implementing the Design Step 8: Opening a Design Checkpoint. Step 2: Defining Constraint Sets and Files. The Processor Configuration Wizard (PCW) within the IP integrator with graphical user interfaces to let you create and modify the PS within the IP integrator block design. 百度云分享 vitis vivado 2021. UG973 - Installing the Vivado Design Suite Tools: 10/27/2021 UG973 - Obtaining and Managing a License: 10/27/2021: Additional Learning Materials. The Vivado In-Depth Tutorials takes users through the design methodology and programming model for building best-in-class designs on all Xilinx devices. Figure 25. Step 2: Synthesizing. It doesn’t do well even on training set of data. 1、在IP这个层面的功能的增强,主要体现在新增加了一个BDC,也就是block design container这个功能,它可以使得我们在一个block里头去实例化另外一个block;. First, I want to start with UVVM-light repo, which only includes util and bfm libraries. prop run. The tutorials provide step by step instructions to perform specific design tasks in the tool using small example designs. Vivado Design Suite Tutorial: Creating and Packaging Custom IP (UG1119) Vivado Design Suite <b. The step to follow for design implementation are summarized below: Click “Create New Project” on the main page Set “Project Name” and “Project Location” Select the type of project Add Source Files Add existing IP (if any) Add constraint file Select FPGA or Board. Step 2: Synthesizing. vivado提供了DDS IP核可以输出正余弦波形,配置方法如下. The model is too simple for the actual trends that are represent in the data. Vivado Design Suite Tutorials - 2021. bat Click File » New Project. This item fits the following BMWs: 1993-1998 E36 BMW 325i 325is 325ic 328i 328is 328ic. The Vitis software platform supports Windows and Linux. 1 in this project, but from what I can tell the same steps should apply in 2021. Each tutorial has a series of independent labs relevant to the tutorial subject matter. Mar 16, 2021 · vivado当前版本2018. 6K Views 13/11/2021. 1 English Revision History Introduction About the Versal ACAP Design Methodology Navigating Content by Design Process System Design Types Design Flows Traditional Design Flows Traditional Design Flow for Hardware-Only Systems. Note: See the accompanying GitHub repo for this blogpost here. Step 5: Saving Constraints. 2、Vivado ML 版支持基于机器学习的. · Basic FPGA Tutorial - ISE v14. Add the IP location as a default IP repository search path under Tools > Settings > IP Defaults. Nov 21, 2022, 2:52 PM UTC a car starts from. 21K subscribers #vivado #xilinx #verilog how to create project in Xilinx Vivado Tutorial | how to do simulation in Xilinx Vivado 2018. Create Vivado Project Start by sourcing the Vivado tools from the command line & launch the Vivado GUI: ~$ source /tools/Xilinx/Vivado/2021. 21K subscribers #vivado #xilinx #verilog how to create project in Xilinx Vivado Tutorial | how to do simulation in Xilinx Vivado 2018. Vitis Integrated Design Environment and Vivado Design Suite¶ Ensure that you have the Vitis™ 2021. 1 2019. UG953 - Vivado Design Suite 7 Series FPGA and Zynq-7000 SoC Libraries Guide. Connecting the Boards and Cables. Vivado modelsim tutorial the lycans queen by laila pdf free download roadrunner email tech support. I'm using Vivado 2022. GPR Exhaust Ktm Duke 890 -R 2021-2022 e5 Deeptone Inox RACE Slip-on. 百度云分享 vitis vivado 2021. 大家好,我是你的好朋友思创斯。今天说一说百度云分享 vitis vivado 2021. Device Architecture Tutorials Learn how to target device-specific features for specific Xilinx architectures using Vivado and any needed low-level software frameworks. Captain Christine Sinclair says she and her teammates won't take the field. Spurious Free Dynamic Range的设置,这个参数与输出数据的. Step 1: Create the Vivado Hardware Design and Generate XSA. Pet Dog Puppy Obedience Training Treat Bait Food Snack Bag Pouch Dispenser. Zynq-7000 Embedded Design Tutorial. Step 1: Opening the Example Project. UVM support for HSV will be coming in a future release. 1 and jumped in. If you do not know how to start with Vitis, then you can follow this; Vitis Beginner Tutorial. Understand the steps required to take their FPGA design from start to finish. Vivado modelsim tutorial the lycans queen by laila pdf free download roadrunner email tech support. 2 2019. 大家好,我是你的好朋友思创斯。今天说一说百度云分享 vitis vivado 2021. ansible shell chdir. 1 2018. 打开IP核配置,parameter Selection选择System Parameters. Feb 06, 2022 · After copying the IP folder to your desired local directory, select Settings from the Flow Navigator window. Navigating Content by Design Process. If you do not know how to start with Vitis, then you can follow this; Vitis Beginner Tutorial. 2 yet. CTM Tutorials tutorial 1 - 12; Proposal Sejarah tema pendidikan; Modul Ulang KAJI BM Kertas 2 SPM 2021 SET 2; Tugasan Kertas Kerja- Konsep Etika Dan Peradaban Menurut Perspektif Islam Dan Barat; Pemantapan Kesepaduan Nasional Malaysia; Kesan Tidak Menutup Aurat; ROLE PLAY Meeting Script 3; 4,0 Implikasi DAN Kepentingan Perlembagaan Persekutuan. 1 in this project, but from what I can tell the same steps should apply in 2021. prop run. 1: Linux Self Extracting Web Installer (BIN - 301. Connect the SZG-SENSOR board to Port A of the XEM8320 (this is important because this is where there reference design files from Opal Kelly expect it to be):. UG763 - Xilinx, Inc. Jun 16, 2021 32 Dislike Share Explore Electronics 7. 21K subscribers #vivado #xilinx #verilog how to create project in Xilinx Vivado Tutorial | how to do simulation in Xilinx Vivado 2018. Third Party Licensing Guide. The Vivado In-Depth Tutorials takes users through the design methodology and programming model for building best-in-class designs on all Xilinx devices. Please inform me or delete this tutorial if there are bad informations! The video should show what happens when you press button2. Getting Started with Zynq This guide is out of date. 1 in this project, but from what I can tell the same steps should apply in 2021. Free shipping. 打开VIVADO,选择IP Catalog. Step 2: Preparing Design Constraints. Step 5: Saving Constraints. 1 2019. but i didn't noticed SDK as part of the installation. Vitis Software Platform and Vivado Design Suite Visit the Xilinx Download Center to download the Vitis software platform. 2、Vivado ML 版支持基于机器学习的. 1 / 4. In other words, when you need to translate your VHDL design into a configuration file to be downloaded into a Xilinx FPGA, you need Vivado framework. Lab Workbook Vivado Tutorial. The Vitis software platform supports Windows and Linux. I'm using Vivado 2022. com Vivado Design Suite Tutorial: Design Analysis and Closure Techniques 2 Se n d Fe e d b a c k. Navigating Content by Design Process. I'm using Vivado 2022. I have not verified it in 2022. Nov 10, 2021. For a list of new features and added device support for all versions, see the Change Log file available with the core in Vivado design tools. Step 5: Saving Constraints. 1 in this project, but from what I can tell the same steps should apply in 2021. To launch the Vivado Design Suite from the Linux or Windows command line, you must install and configure the tool to run on the local machine. 输入DDS,找到DDS IP核,双击打开. Connect the SZG-SENSOR board to Port A of the XEM8320 (this is important because this is where there reference design files from Opal Kelly expect it to be):. Vitis Software Platform and Vivado Design Suite Visit the Xilinx Download Center to download the Vitis software platform. csv文件,这个表与vivado hardware manager中的器件一致。. Jun 16, 2021 32 Dislike Share Explore Electronics 7. 1 English Versal ACAP Hardware, IP, and Platform Development Methodology Guide (UG1387) Document ID UG1387 Release Date 2021-07-26 Version 2021. You'll need an internet connection initially to refresh and see the current version of the Xilinx Board Store and download the presets for your desired boards. Date. vivado #vitis #modelSim #questaSim #simulator #verilog #vhdl #fpga #productivity #programming #coding #xilinx #amd #shortsA quick . 1 2018. After that, you'll be able to work with them offline. 大家好,我是你的好朋友思创斯。今天说一说百度云分享 vitis vivado 2021. Step 3: Creating Timing Constraints. FLATTEN_HIERARCHY}= {full}. 3 2018. This is already done in the test bench. Captain Christine Sinclair says she and her teammates won't take the field. Open the Vivado® Design Suite. Step 5: Saving Constraints. Step 3: Creating Timing Constraints. Nov 21, 2022, 2:52 PM UTC a car starts from. UG763 - Xilinx, Inc. Connect the SZG-SENSOR board to Port A of the XEM8320 (this is important because this is where there reference design files from Opal Kelly expect it to be):. Add Source files in Vivado Project. Device Architecture Tutorials Learn how to target device-specific features for specific Xilinx architectures using Vivado and any needed low-level software frameworks. In other words, when you need to translate your VHDL design into a configuration file to be downloaded into a Xilinx FPGA, you need Vivado framework. 1 2019. Step 1. The tutorials provide step by step instructions to perform specific design tasks in the tool using small example designs. pdf with my test block design ; Check the git hub link with test block design files----Details. Each tutorial has a series of independent labs relevant to the tutorial subject matter. We will start from a ZCU104 preset design, add platform required peripherals and configure them. Using the Netlist Insertion Method to Debug a Design. Looking through the syllabus I know I'll be learning VHDL with the help of a Cora Z7 board and Vivado software. Pearson’s wife, Judy Carlick Pearson, told The Northern View the past two years don’t seem like a long time. 1 in this project, but from what I can tell the same steps should apply in 2021. pdf

Aug 24, 2021. Prerequisites Skills Basic familiarity with Vivado. 'vivado' is not recognized as an internal or external command, operable program or batch file. Figure 25. shoalwater boat parts, what does a decomposing body smell like reddit

As an FPGA Software Applications Engineer, lead various Vivado Design Suite Tools - Synthesis, Simulation and implementation power tools. . Vivado tutorial 2021

change the ssltls server configuration to only allow strong key exchanges

change the ssltls server configuration to only allow strong key exchanges

UG1118 - Vivado Design Suite User Guide: Creating and Packaging Custom IP. Fifty-eight-year-old tug captain Troy Pearson and 25-year-old crew member Charley Cragg died, while a third crew member survived, when the tug Ingenika went down in a storm in February 2021 while towing a barge. 1 2018. Using the Netlist Insertion Method to Debug a Design. Open the Vivado tool -> IP Catalog, right-click on UltraScale FPGAs Transceivers Wizard and select Compatible Families. 1 and jumped in. Give the project the desired name and specify the desired file path. Hardware Setup. 2 English Versal ACAP Hardware, IP, and Platform Development Methodology Guide (UG1387) Document ID UG1387 Release Date 2021-11-19 Version 2021. Preparing the Tutorial Design Files. 找到“Text Editor”,并在右侧Current Editor下拉找到Custom Editor,并点击右侧的三个小点,选择路径;. December 24, 2021 Surf-VHDL VHDL. - Brought-up first SystemVerilog support in Xilinx. Click Finish to create the Vivado project. Dec 24, 2021 · This post reports how to create a project on Vivado including the VHDL design files. ② PC=PC+4+立即数*4,执行的. tcl using the below command in Linux/Windows. com/go/woocommerce ️️ PASO 3: Instal. Logic design and Verilog are the bases of this tutorial. 输入DDS,找到DDS IP核,双击打开. 1 and jumped in. 2) November 17, 2021 See all versions of this document Xilinx is creating an environment where employees, customers, and partners feel welcome and included. 2 yet. 1 ML ; Check. Nov 16, 2022 · Step 1: Creating a Project with the Vivado New Project Wizard Step 2: Synthesize, Implement, and Generate the Bitstream Using the Synplify Pro Synthesis Tool and Vivado Design Suite to Debug a Design Step 1: Create a Synplify Pro Project Step 2: Synthesize the Synplify Project Step 3: Create DCPs for the Black Box Created in Synplify Pro. If you do not know how to start with Vitis, then you can follow this; Vitis Beginner Tutorial. Add a MultiCycle Path. UG998 - Introduction to FPGA Design Using High-Level Synthesis. (Last updated on: 9 April, 2021) How to start a new Vivado project to create a testbench for programming with Verilog or VHDL languages. 输入DDS,找到DDS IP核,双击打开. tools, see the Vivado Design Suite Tutorial: Design Flows Overview (UG888). UG973 - Installing the Vivado Design Suite Tools: 10/27/2021 UG973 - Obtaining and Managing a License: 10/27/2021: Additional Learning Materials. This course covers everything from the very basics to the more complex topics. UG953 - Vivado Design Suite 7 Series FPGA and Zynq-7000 SoC Libraries Guide. We have showed demo with PYNQ Z1 FPGA board on thi. Vivado Design Suite Tutorial: Creating and Packaging Custom IP (UG1119) Vivado Design Suite <b. Vivado 2021. Navigating Content by Design Process. (August 2021) The Philippine Physician Licensure Examination, also called Philippine Medical Boards, is the professional licensure examination for incoming physicians in the Philippines, exclusively administered twice a year by the. Jun 03, 2021 · UG973 - Vivado Design Suite Release Notes, Installation, and Licensing Guide. The tutorials provide step by step instructions to perform specific design tasks in the tool using small example designs. If you install the Vitis IDE, you will automatically get both the Vivado Design Suite and the Vitis IDE. Step 4: Using the Constraints Editor. This article includes a list of general references, but it lacks sufficient corresponding inline citations. 1 2020. Implement a micro blaze softcore processor on their FPGA. 百度云分享 vitis vivado 2021. 找到“Text Editor”,并在右侧Current Editor下拉找到Custom Editor,并点击右侧的三个小点,选择路径;. 1 English Versal ACAP Hardware, IP, and Platform Development Methodology Guide (UG1387) Document ID UG1387 Release Date 2021-07-26 Version 2021. grandpa cums in pussy. 2 yet. Create Vivado Project Start by sourcing the Vivado tools from the command line & launch the Vivado GUI: ~$ source /tools/Xilinx/Vivado/2021. UG953 - Vivado Design Suite 7 Series FPGA and Zynq-7000 SoC Libraries Guide. Hardware Setup. 2 2019. ansible shell chdir. This file provides the Vivado Design Suite with MicroZed configuration information. 1 unified software development platform installed. aetna deductible waived meaning. December 24, 2021 Surf-VHDL VHDL. The step to follow for design implementation are summarized below: Click "Create New Project" on the main page Set "Project Name" and "Project Location" Select the type of project Add Source Files Add existing IP (if any) Add constraint file Select FPGA or Board. Vivado Design Suite Tutorials - 2021. 1 2018. Photo by Volodymyr Hryshchenko / Unsplash. For standalone simulation in Vivado you can source run_xsim. Analyze the Current Constraints Files. The Save Checkpoint As dialog box opens and you can specify a name for the checkpoint file to write to disk. 百度云分享 vitis vivado 2021. integrated design environment (IDE). Each tutorial has a series of independent labs relevant to the tutorial subject matter. 2 yet. The Vivado In-Depth Tutorials takes users through the design methodology and programming model for building best-in-class designs on all Xilinx devices. The example above represents under- fitting in regression. vectric clipart free download. 100 mbps speed is good or bad. UG900 - Vivado Design Suite User Guide: Logic Simulation. Click on the various links to see what information they provide and which allows you to change the synthesis settings. 1 2020. 4 , all OS(win和linux)「建议收藏」 思创斯忠实用户-ss • 2022年12月28日 16:31 • 未分类 • 阅读 10. Date. 100 mbps speed is good or bad. 1 2019. This support starts from the moment an investigator first makes contact with a victim, through to the. In my case, the directory is loacated at C:\Xilinx\Vivado\2013. It is very common with the students, who are trying to learn a new programming language, to only read and understand the codes on the books or online. Step 4: Using the Constraints Editor. 2 English. Vivado V2017. Beginners' tutorials for VHDL on Xilinx Vivado I will be taking my first-ever FPGA class this fall. 大家好,我是你的好朋友思创斯。今天说一说百度云分享 vitis vivado 2021. Running the Set Up Debug Wizard. 79K subscribers This Video is on "how to create Vitis/VIVADO 2020. 4 , all OS(win和linux)「建议收藏」 思创斯忠实用户-ss • 2022年12月28日 16:31 • 未分类 • 阅读 10. Step 4: Modify the IP Definition. Step 4: Using the Constraints Editor. Join Whitney Knitter of Knitronics as she walks you through the installation of Xilinx's FPGA Design IDE on Ubuntu LTS Linux distribution. We have showed demo with PYNQ Z1 FPGA board on thi. By using this site, you agree to the aluminum auto trim restoration near me and home assistant device. pdf

Aug 24, 2021. Once software has been downloaded, you will open a new project. 1 2018. Vivado modelsim tutorial the lycans queen by laila pdf free download roadrunner email tech support. Vivado Project Tutorial. zip_Xilinx ZYNQ _similarerq_ vivado _ vivado 最新发布 09-23 xilinx板子配置,包括zynq等,在vivaodo里面没有,需要自行 添加 vivado添加 文件之后出现non-module file的问题 wind 3323. Creating a base directoryThis project tutorial can be placed in any location on your. 0 May 25, 2022 Version for SAP S/4HANA 2021 FPS02. Step 1. For instance, the --vivado switch can configure optimization, placement, and timing, or set up. 3 2018. 2、Vivado ML 版支持基于机器学习的. Step 2: Defining Constraint Sets and Files. Note: Starting June 1, 2021, GoDaddy will no longer issue or renew Code Signing or Driver Signing Certificates. Lab 1: Defining Timing Constraints and Exceptions. Key Concepts. The Vitis software platform comes with all the hardware and software as a package. This video mainly shows how to create a hello_world project and boot. This tutorial is based on Vitis Unified Software Development 2020. Nov 2, 2021. . jubity music download